## ICePAK™ Power Module

### P-Channel and N-Channel Power MOSFFT in a Three-Phase Bridge Configuration

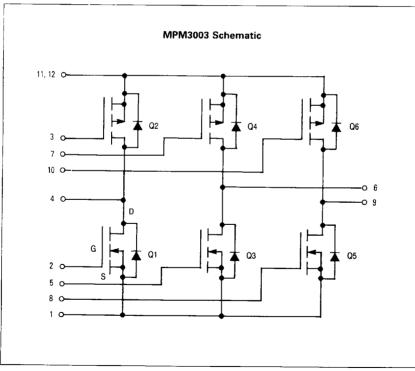

The MPM3003 is a three-phase bridge power circuit packaged in the new power SIP called the ICePAK package. The upper legs of the bridge consist of three P-Channel power MOSFETs and the lower legs of the bridge consist of three N-Channel power MOSFETs. This power circuit is ideal for applications such as disk drives, servo motor drives and stepper motor controls.

Features of this product include:

- P and N-Channel Power MOSFFTs for Fase of Drive

- · Isolated Package with 2 kV Isolation Voltage Rating

- High Peak Current Handling Capability 25 Amperes

- · Avalanche Energy Capability is Specified

- · Compact Space Saving Package

- · Excellent Thermal Capability

- Interface Directly with MC33033 and MC33035 Brushless dc Motor Control ICs

### **MPM3003**

Motorola Preferred Device

TMOS POWER MOSFET **3-PHASE BRIDGE** 10 AMPERES **60 VOLTS**

ICePAK is a trademark of Motorola, Inc.

TMOS is a registered trademark of Motorola, Inc.

Preferred devices are Motorola recommended choices for future use and best overall value.

REV 1

13

### MAXIMUM RATINGS (T,j = 25°C unless otherwise noted)

| Rating                                                    |                   | Symbol                            | Value               | Unit  |  |

|-----------------------------------------------------------|-------------------|-----------------------------------|---------------------|-------|--|

| Drain-to-Source Voltage                                   | (All Types)       | V <sub>DSS</sub>                  | 60                  | Volts |  |

| Drain-to-Gate Voltage (R <sub>GS</sub> = 1.0 M $\Omega$ ) | (All Types)       | VDGR                              | V <sub>DGR</sub> 60 |       |  |

| Gate-to-Source Voltage — Continuous — Non-Repetitive      | VGS               | ±20<br>±40                        |                     |       |  |

| Drain Current — Continuous<br>— Pulsed                    | (Any 2 Devices)   | I <sub>D</sub>                    | 10<br>25            | Amps  |  |

| RMS Isolation Voltage                                     | (Any Pin to Case) | V <sub>ISO</sub>                  | 2000                | Volts |  |

| Operating and Storage Temperature Range                   |                   | T <sub>J</sub> , T <sub>stg</sub> | -40 to 150          | °C    |  |

### UNCLAMPED DRAIN-TO-SOURCE AVALANCHE CHARACTERISTICS — ALL TYPES (TJ $\leq$ 150°C)

| [ | Unclamped Drain-to-Source Avalanche Energy — T <sub>J</sub> = 25°C | W <sub>DSS</sub> <sup>(1)</sup> | 250 | mJ | ĺ |

|---|--------------------------------------------------------------------|---------------------------------|-----|----|---|

| ] | T <sub>.I</sub> = 100°C                                            |                                 | 40  |    |   |

| ١ | Repetitive Pulse Drain-to-Source Avalanche Energy                  | W <sub>DSS</sub> (2)            | 3.1 |    | l |

### THERMAL CHARACTERISTICS

| Power Dissipation — T <sub>C</sub> = 25°C<br>(Any Single P-Channel)<br>(Any Single N-Channel)                                | P <sub>D</sub>      | 42<br>31         | Watts |

|------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------|-------|

| Power Derating — Derate above T <sub>C</sub> = 25°C<br>(Any Single P-Channel)<br>(Any Single N-Channel)                      | 1/R <sub>0</sub> JC | 0.33<br>0.25     | °C/W  |

| Thermal Resistance — Junction to Case (Any Single P-Channel) — Junction to Case (Any Single N-Channel) — Junction-to-Ambient | R <sub>BJA</sub>    | 3.0<br>4.0<br>35 | °C/W  |

| Maximum Lead Temperature for Soldering Purposes 1/8" from case for 10 seconds                                                | Τ <sub>L</sub>      | 260              | ³C    |

### **ELECTRICAL CHARACTERISTICS** ( $T_C = 25^{\circ}C$ unless otherwise noted)

| Characteristic                                                                                |                     | Symbol               | Min | Тур   | Max       | Unit |

|-----------------------------------------------------------------------------------------------|---------------------|----------------------|-----|-------|-----------|------|

| OFF CHARACTERISTICS                                                                           |                     |                      |     |       |           |      |

| Drain-to-Source Breakdown Voltage<br>(VGS = 0, I <sub>D</sub> = 0.25 mA)                      | (All Devices)       | V <sub>(BR)DSS</sub> | 60  | _     | _         | Vdc  |

| Zero Gate Voltage Drain Current<br>(VDS = 60 V, VGS = 0)<br>(VDS = 60 V, VGS = 0, TJ = 125°C) | (Any Single Device) | DSS                  | _   | _<br> | 10<br>100 | μAdc |

| Gate-Body Leakage Current — Forward (VGSF = 20 Vdc, VDS = 0)                                  | (Any Single Device) | <sup>I</sup> GSSF    |     |       | 100       | nAdc |

| Gate-Body Leakage Current — Reverse (VGSR = 20 Vdc, VDS = 0)                                  | (Any Single Device) | GSSR                 | _   | _     | 100       | nAdc |

(1)  $V_{DD}=45$  V,  $I_{D}=10$  A (2)  $V_{DD}=45$  V,  $I_{D}=10$  A, f=10 kHz Note 1: Handling precautions to protect against electrostatic discharge is mandatory.

(continued)

### **ELECTRICAL CHARACTERISTICS** — continued (T<sub>C</sub> = 25°C unless otherwise noted)

| Ch                                                                               | aracteristic                                                              | Symbol              | Min        | Тур           | Max         | Unit     |

|----------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------|------------|---------------|-------------|----------|

| ON CHARACTERISTICS*                                                              |                                                                           | -4                  |            |               | -           |          |

| Gate Threshold Voltage<br>(VDS = VGS, ID = 1.0 mAdc)<br>(TJ = 125°C)             | (All Devices)                                                             | V <sub>GS(th)</sub> | 2.0<br>1.5 | 3.0           | 4.5<br>4.0  | Vdc      |

| Static Drain-to-Source On-Resist<br>(VGS = 10 Vdc, I <sub>D</sub> = 5.0 Adc)     | ance (Q2, Q4 and Q6)                                                      | rDS(on)             | _          | 0.11          | 0.15        | Ohms     |

| Drain-to-Source On-Voltage (VGS<br>(ID = 10 A)<br>(ID = 5.0 A, TJ = 125°C)       | s = 10 Vdc) (Q2, Q4 and Q6)                                               | V <sub>DS(on)</sub> |            | _             | 1.5<br>1.4  | Vdc      |

| Static Drain-to-Source On-Resista<br>(VGS = 10 Vdc, I <sub>D</sub> = 5.0 Adc)    | ance (Q1, Q3 and Q5)                                                      | rDS(on)             | _          | 0.22          | 0.28        | Ohms     |

| Drain-to-Source On-Voltage (VGS<br>(ID = 10 A)<br>(ID = 5.0 A, TJ = 125°C)       | S = 10 Vdc) (Q1, Q3 and Q5)                                               | V <sub>DS(on)</sub> | _          | _             | 2.8<br>2.7  | Vdc      |

| Forward Transconductance<br>(V <sub>DS</sub> = 15 Vdc, I <sub>D</sub> = 5.0 Adc) | (Q2, Q4 and Q6)                                                           | 9FS                 | 4.0        | _             | _           | Mhos     |

| Forward Transconductance<br>(VDS = 15 Vdc, ID = 5.0 Adc)                         | (Q1, Q3 and Q5)                                                           | 9FS                 | 2.0        |               | _           | Mhos     |

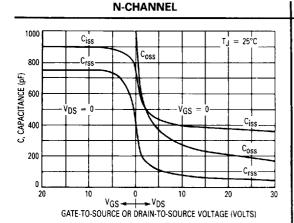

| DYNAMIC CHARACTERISTICS (A                                                       | il Types)                                                                 |                     | <u> </u>   |               | L           | ı        |

| Input Capacitance                                                                |                                                                           | Ciss                |            |               | 900         | pF       |

| Output Capacitance                                                               | $(V_{DS} = 25 \text{ V. } V_{GS} = 0$<br>f = 1.0 MHz)                     | Coss                | <b> </b>   |               | 750         | 1        |

| Transfer Capacitance                                                             | ]                                                                         | C <sub>rss</sub>    | _          |               | 200         |          |

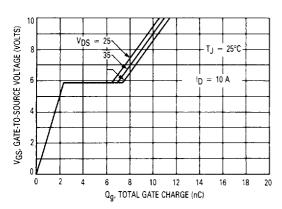

| SWITCHING CHARACTERISTICS                                                        | (N-Channel, Q2, Q4 and Q6)                                                | <u> </u>            |            |               |             | l .      |

| Turn-On Delay Time                                                               |                                                                           | <sup>t</sup> d(on)  | T -        | _             | 20          | ns       |

| Rise Time                                                                        | $(V_{DD} = 25 \text{ V}, I_{D} = 5.0 \text{ A})$                          | tr                  | _          | _             | 40          |          |

| Turn-Off Delay Time                                                              | R <sub>gen</sub> = 50 Ohms)                                               | <sup>t</sup> d(off) |            | _             | 40          |          |

| Fall Time                                                                        |                                                                           | tf                  |            |               | 45          |          |

| Total Gate Charge                                                                | N 10 V 1 10 1                                                             | Qg                  | _          | 12            | 17          | nC       |

| Gate-Source Charge                                                               | $V_{DS} = 48 \text{ V, } I_{D} = 10 \text{ A}$<br>$V_{GS} = 10 \text{ V}$ | Qgs                 |            | 6.5           | _           |          |

| Gate-Drain Charge                                                                |                                                                           | Q <sub>gd</sub>     | _          | 5.5           | _           |          |

| SWITCHING CHARACTERISTICS                                                        | (P-Channels, Q1, Q3 and Q5)                                               |                     |            | •             |             | <u> </u> |

| Turn-On Delay Time                                                               |                                                                           | t <sub>d(on)</sub>  | _          | _             | 20          | ns       |

| Rise Time                                                                        | (V <sub>DD</sub> = 25 V, I <sub>D</sub> = 5.0 A                           | t <sub>r</sub>      |            |               | 150         |          |

| Turn-Off Delay Time                                                              | R <sub>gen</sub> = 50 Ohms)                                               | <sup>t</sup> d(off) |            | _             | 100         |          |

| Fall Time                                                                        |                                                                           | t <sub>f</sub>      |            | _             | 100         |          |

| Total Gate Charge                                                                | ()(= 0 = 48 V  = = 10 A                                                   | Qg                  | _          | 28            | 35          | nC       |

| Gate-Source Charge                                                               | (V <sub>DS</sub> = 48 V. I <sub>D</sub> = 10 A<br>V <sub>GS</sub> = 10 V) | Q <sub>gs</sub>     |            | 15            | _           |          |

| Gate-Drain Charge                                                                | Q <sub>gd</sub>                                                           |                     | 13         |               |             |          |

|                                                                                  | TERISTICS* (N-Channels, Q2, Q4 and Q6)                                    |                     |            |               |             |          |

| Forward On-Voltage                                                               | (I <sub>S</sub> = 10 A)                                                   | V <sub>SD</sub>     |            | 1.0           | _           | Vdc      |

| Forward Turn-On Time                                                             | (I <sub>S</sub> = 10 A, V <sub>r</sub> = 25 V, di/dt = 100 A/usec)        | ton                 | Lir        | nited by stra | y inductano | e        |

| Reverse Recovery Time                                                            |                                                                           | t <sub>rr</sub>     |            | 50            |             | ns       |

|                                                                                  | TERISTICS* (P-Channels, Q1, Q3 and Q5)                                    |                     |            |               |             |          |

| Forward On-Voltage                                                               | (I <sub>S</sub> = 10 A)                                                   | V <sub>SD</sub>     |            | 4.0           |             | Vdc      |

| Forward Turn-On Time                                                             | (I <sub>S</sub> = 10 A, V <sub>r</sub> = 25 V, di/dt = 100 A/µsec)        | ton                 | Lir        | nited by stra | y inductano | e        |

| Reverse Recovery Time                                                            | , , , , , , , , , , , , , , , , , , , ,                                   | t <sub>rr</sub>     | _          | 300           |             | ns       |

| Indicatos Dulas Test. Dulas Mish. 000                                            |                                                                           |                     |            |               |             |          |

<sup>\*</sup>Indicates Pulse Test: Pulse Width = 300 µs Max, Duty Cycle ≤ 2.0%.

Note 1: Handling precautions to protect against electrostatic discharge is mandatory.

Suggested Heat Sink: Thermalloy, Inc. Heatsink #18246

# 13

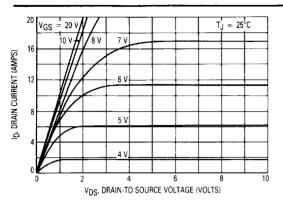

### TYPICAL CHARACTERISTICS

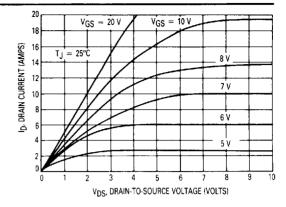

Figure 1. On-Region Characteristics

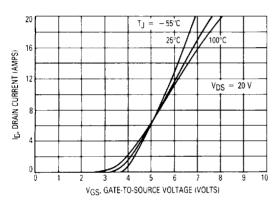

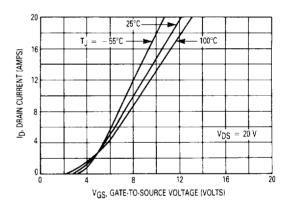

Figure 3. Transfer Characteristics

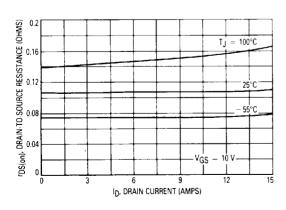

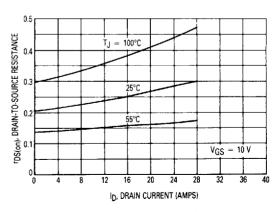

Figure 5. On-Resistance versus Drain Current

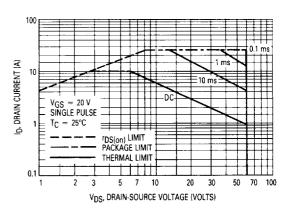

### P-CHANNEL

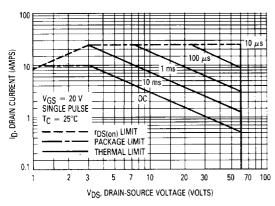

Figure 2. On-Region Characteristics

Figure 4. Transfer Characteristics

Figure 6. On-Resistance versus Drain Current

6367254 0103171 947

#### TYPICAL CHARACTERISTICS

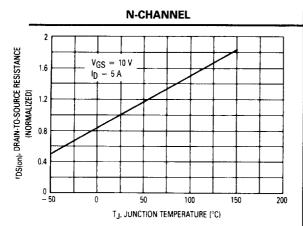

Figure 7. On-Resistance Variation

With Temperature

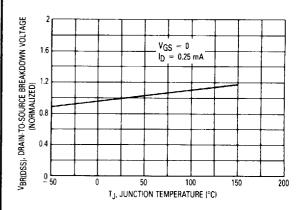

Figure 9. Breakdown Voltage Variation With Temperature

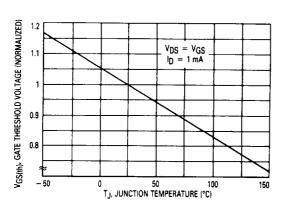

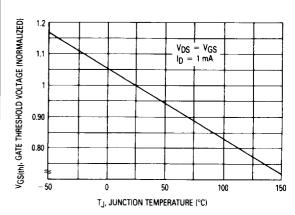

Figure 11. Gate-Threshold Voltage Variation With Temperature

P-CHANNEL

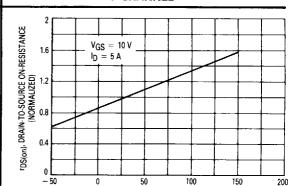

Figure 8. On-Resistance Variation With Temperature

TJ, JUNCTION TEMPERATURE (°C)

Figure 10. Normalized Breakdown Voltage versus Temperature

Figure 12. Gate-Threshold Voltage Variation With Temperature

### 13

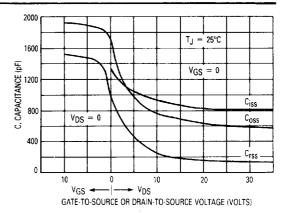

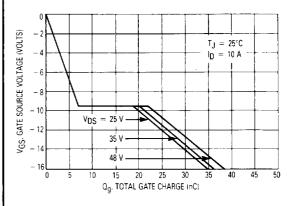

### TYPICAL CHARACTERISTICS

Figure 13. Capacitance Variation

Figure 15. Gate Charge versus Gate-to-Source Voltage

Figure 17. Maximum Rated Forward Biased Safe Operating Area

### P-CHANNEL

Figure 14. Capacitance Variation

Figure 16. Gate Charge versus Gate-to-Source Voltage

Figure 18. Maximum Rated Forward Biased Safe Operating Area

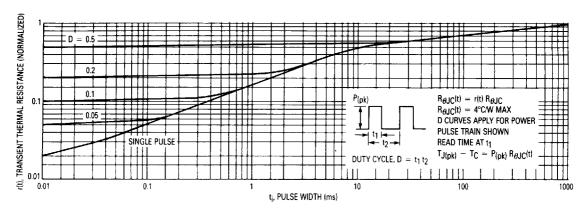

Figure 19. Thermal Response (N-Channel)

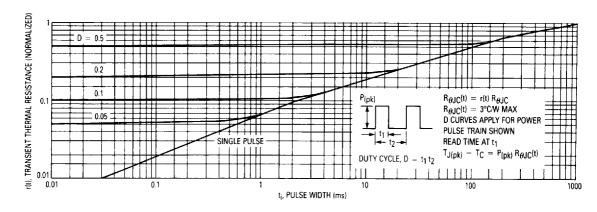

Figure 20. Thermal Response (P-Channel)

### **FORWARD BIASED SAFE OPERATING AREA**

The FBSOA curves define the maximum drain-to-source voltage and drain current that a device can safely handle when it is forward biased, or when it is on, or being turned on. Because these curves include the limitations of simultaneous high voltage and high current, up to the rating of the device, they are especially useful to designers of linear

systems. The curves are based on a case temperature of 25°C and a maximum junction temperature of 150°C. Limitations for repetitive pulses at various case temperatures can be determined by using the thermal response curves. Motorola Application Note, AN569, "Transient Thermal Resistance-General Data and Its Use" provides detailed instructions.

### **COMMUTATING SAFE OPERATING AREA (CSOA)**

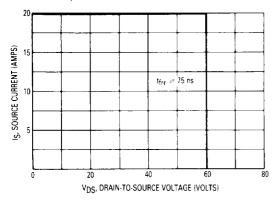

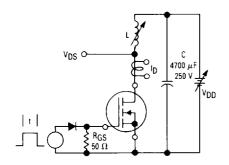

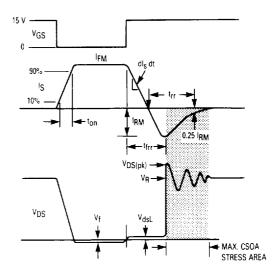

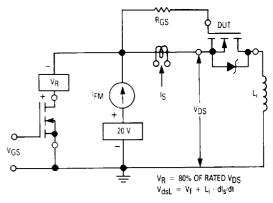

The Commutating Safe Operating Area (CSOA) of Figure 22 defines the limits of safe operation for commutated source-drain current versus re-applied drain voltage when the source-drain diode has undergone forward bias. The curve shows the limitations of IFM and peak Vp for a given commutation speed. It is applicable when waveforms similar to those of Figure 21 are present. Full or half-bridge PWM DC motor controllers are common applications requiring CSOA data.

The time interval  $t_{frr}$  is the speed of the commutation cycle. Device stresses increase with commutation speed, so  $t_{frr}$  is specified with a minimum value. Faster commutation speeds require an appropriate derating of  $I_{FM}$ , peak  $V_{Fl}$  or both. Ultimately,  $t_{frr}$  is limited primarily by device, package, and circuit impedances. Maximum device stress occurs during  $t_{rr}$  as the diode goes from conduction to reverse blocking.

V<sub>DS(pk)</sub> is the peak drain-to-source voltage that the device must sustain during commutation; I<sub>FM</sub> is the maximum forward source-drain diode current just prior to the onset of commutation.

$V_{\mbox{\footnotesize{R}}}$  is specified at 80% of  $V_{\mbox{\footnotesize{(BR)DSS}}}$  to ensure that the CSOA stress is maximized as IS decays from IRM to zero.

RGS should be minimized during commutation. T<sub>J</sub> has only a second order effect on CSOA.

Stray inductances,  $L_{\hat{i}}$  in Motorola's test circuit are assumed to be practical minimums.

Figure 22. Commutating Safe Operating Area (CSOA)

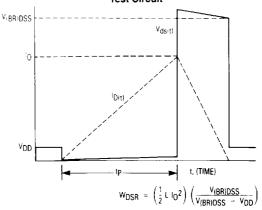

Figure 24. Unclamped Inductive Switching Test Circuit

Figure 21. Commutating Waveforms

Figure 23. Commutating Safe Operating Area Test Circuit

Figure 25. Unclamped Inductive Switching Waveforms

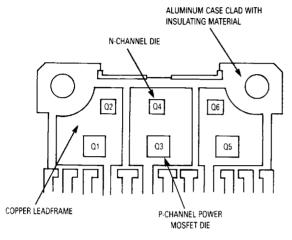

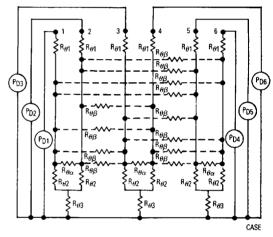

The MPM3003 consists of three n-channel and p-channel pairs die bonded to three separate copper leadframes. An insulating material isolates the leadframes from the aluminum case. The internal construction is shown in Figure 26 below.

Figure 26. Internal Construction of the MPM3003

From this configuration, the thermal model shown in Figure 27 can be derived. Equation 3 is derived from this model.  $\alpha$  is defined as the coupling coefficient between adjacent die on a common leadframe and  $\beta$  is defined as the coupling coefficient between die on separate leadframes.

#### **EQUATION 3.**

$$T_{Ji} = T_{C} + P_{Di} R_{\theta JC} + \sum_{k=1}^{6} \alpha_{ik} P_{Dk} R_{\theta JC} + \sum_{k=1}^{6} \beta_{ik} P_{Dk} R_{\theta JC}$$

$\alpha$  and  $\beta$  values for different die combinations are listed in the maximum ratings. As an example of how the equation is used, assume that devices Q1 and Q4 are dissipating 10 watts each at a case temperature of 25°C, then calculate the junction temperature of Q1 through Q6.

FROM EQUATION 3.

$$\begin{split} T_{J1} &= T_C + P_{D1} \ R_{\theta J C1} + \beta_{14} \ P_{D4} \ R_{\theta J C4} \\ &= 25 + (10)(3) + (.01)(10)(4) = 55.4^{\circ}C \\ T_{J2} &= T_C + \alpha_{22} \ P_{D1} \ R_{\theta J C1} + \beta_{24} \ P_{D4} \ R_{\theta J C4} \\ &= 25 + .5(10)(3) + .30(10)(4) = 52^{\circ}C \\ T_{J3} &= T_C + \alpha_{34} \ P_{D4} \ R_{\theta J C4} + \beta_{31} \ P_{D1} \ R_{\theta J C1} \\ &= 25 + .5(10)(4) + (.3)(10)(3) = 55^{\circ}C \\ T_{J4} &= T_C + P_{D4} \ R_{\theta J C4} + \alpha_{41} \ P_{D1} \ R_{\theta J C1} \\ &= 25 + (10)(4) + (.01)(10)(3) = 65.3^{\circ}C \\ T_{J5} &= T_C + \alpha_{54} \ P_{D1} \ R_{\theta J C4} + \beta_{51} \ P_{D1} \ R_{\theta J C1} \\ &= 25 + 0(10)(4) + 0(10)(3) = 25^{\circ}C \\ T_{J6} &= T_C + \alpha_{64} \ P_{D4} \ R_{\theta J C4} + \beta_{61} \ P_{D1} \ R_{\theta J C1} \\ &= 25 + .5(10)(4) + 0(10)(3) = 45^{\circ}C \\ \end{split}$$

Figure 27. Thermal Model of the MPM3003

$R_{\theta 1}$  = junction to leadframe thermal resistance  $R_{\theta 2}$  = leadframe to isolator thermal resistance

R<sub>63</sub> = isolator to case thermal resistance

$R_{\theta\alpha}$  = coupling thermal resistance between adjacent die on common leadframe

on common leading me

$R_{\theta\beta}~=~$  coupling thermal resistance between die on

separate leadframes

$R_{\rm BJC} = R_{\rm B1} + R_{\rm B2} + R_{\rm B3}$

### **Table 1. Thermal Coupling Coefficients**

$\alpha$  = coupling coefficient between adjacent die on same leadframe  $\beta$  = coupling coefficient between die on separate leadframes A:  $\alpha$  coefficient values:  $\alpha_{12} = \alpha_{21} = \alpha_{34} = \alpha_{43} = \alpha_{56} = \alpha_{65} = 0.5$  B:  $\beta$  coefficient values  $\beta_{11} = \beta_{22} = \beta_{33} = \beta_{44} = 0$   $\beta_{12} = \beta_{21} = \beta_{34} = \beta_{43} = \beta_{56} = \beta_{65} = 0$   $\beta_{16} = \beta_{61} = \beta_{25} = \beta_{52} = 0$   $\beta_{23} = \beta_{32} = \beta_{14} = \beta_{41} = \beta_{36} = \beta_{63} = \beta_{45} = \beta_{54} = .01$   $\beta_{24} = \beta_{42} = \beta_{46} = \beta_{64}$   $\beta_{13} = \beta_{31} = \beta_{35} = \beta_{53}$  3.30

13

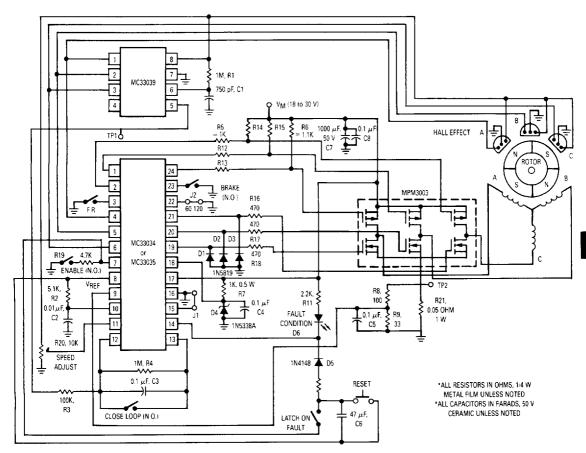

### BRUSHLESS DC MOTOR CONTROL SYSTEM USING THE MPM3003, MC33035, AND MC33039

Brushless DC motors are becoming very popular due to their linear speed-torque characteristics, lack of brush wear and brush arcing, reduced EMI, thermal efficiency, small size for a given horsepower, and capability of operating at high RPM. However, the cost of the control circuitry needed to electronically commutate the field has slowed proliferation of brushless motor control systems. Recent developments in linear ICs and power MOSFETs have substantially lowered the cost, size, and complexity of the brushless DC motor controllers, making brushless systems more viable.

The MC33035 control IC is the control center of the system illustrated in Figure 28. It decodes the Hall effect signals that indicate motor position and generates the proper firing of the six output transistors, which are neatly housed in the MPM3003. Ancillary functions such as braking, fault recognition, pulse width modulation of the lower transistors for speed control, and forward/reverse selection are also handled by the MC33035.

For closed loop operation the MC33035 requires an input voltage proportional to motor speed. The traditional approach is to use a tachometer to generate the required

voltage. Adding the MC33039 to the system allows closed loop speed control without the added cost of a tachometer. Hall effect signals are fed into the MC33039, where each positive and negative going edge is detected. For each transition in any of the three inputs the MC33039 generates an output pulse whose width is set by an external RC network. Since increased pulse density at the MC33039 output indicates higher motor speed, integrating its output gives a voltage proportional to motor speed. The filtered signal is fed into the MC33035 and processed to help define the gate drive pulse width of the motor's drive transistors.

The MPM3003 is a nice fit for the application because its MOSFETs can handle surge currents up to 25 A. High currents are likely at start-up, during braking, or upon an abrupt change in the direction of motor rotation. A current feedback loop in the MC33035 can be set to limit peak motor currents (but not during braking).

The system illustrated in Figure 28 is designed for a motor with 120 degree Hall effect sensor spacing. The system can easily be changed to accommodate 60 degree spacing by removing the jumper at Pin 22.

Figure 28. 24 V Brushless Motor Drive

### THREE PHASE BRUSHLESS MOTOR DRIVE DESIGN CONSIDERATIONS

- N-Channel Drive: Very high switching speeds are not needed and are often undesirable in brushless motor control systems. The N-channel MOSFETs of the MPM3003 require little gate charge to turn on, therefore gate drives with low output impedance generate unnecessarily fast switching speeds. These fast switching times will increase switching noise and may increase the stress on the power transistors. It was determined that a gate drive impedance in the 470 to 1000 Ohm range yields a good compromise between low switching losses and low noise.

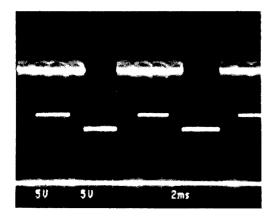

- P-Channel Drive: A common pitfall in designing the drive for the P-channel devices in a brushless motor control system is to assume that since the P-channel MOSFETs are switching at the motor commutation frequency, (a frequency much lower than the PWM frequency) they do not need a low impedance gate drive. What is often overlooked is that whenever the drain-to-source voltage changes (due to a greater switching frequency of the N-channel devices in the lower legs the bridge, see Figure 29), the upper gate drive must charge and discharge the gate-to-drain capacitance of the P-channel devices. If the gate drive is insufficient, the P-channel devices will briefly turn on, causing a shoot through current that dramatically increases switching losses. Figure 29 shows undesirable noise on the gate of the P-channels gate due to fast switching N-channels and a high impedance in the gates of the P-channels in the circuit shown in Figure 28.

Avoiding shoot through currents can be accomplished by increasing the turn on time of the N-channel devices to limit the impressed dv/dt's and keeping the P-channel gate drive impedance low, especially in the off state. Adding capacitance across the P-channel gate-to-source (a 0.01  $\mu\text{F}$  capacitor worked well in the circuit of Figure 28) is a simple way to give the gate drive a reservoir of charge that keeps the gate off when  $C_{gd}$  demands a displacement current. The added capacitance will increase the turn on and turn off delay times but will not greatly after the drain-to-source voltage rise and fall times.

Figure 29. Gate Voltage Waveforms

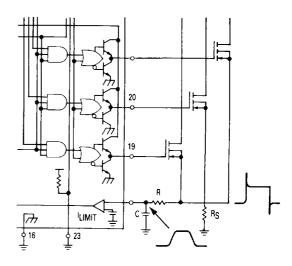

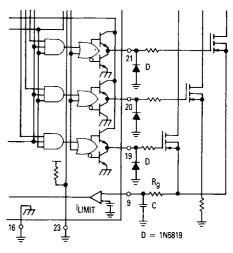

Current Waveform Spike Suppression: The addition of the RC filter shown in Figure 30 will eliminate the current limit instability caused by the leading edge spike on the current waveform. The resistor should be a low inductance type.

Figure 30. Current Waveform Spike Suppression

Damping MOSFET Oscillations: Series gate resistors shown in Figure 31 will damp any high frequency oscillations caused by the MOSFET capacitance and stray inductance. Diode D is required if the negative current into the Bottom Drive Output of the MC33035 exceeds 5.0 mA.

Figure 31. Damping MOSFET Oscillations

13

### MPM3003 30 MOTOR CONTROLLER

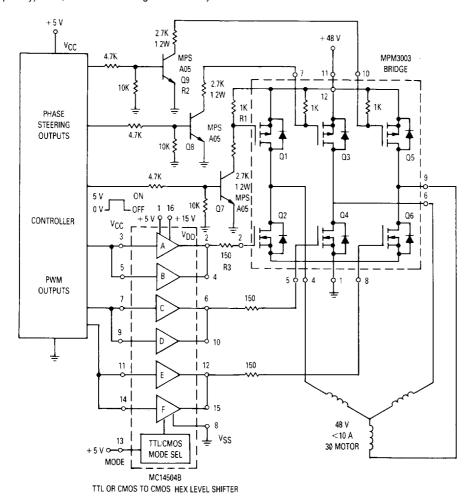

The integration of the three N-channel and the three P-Channel power MOSFETs into the MPM3003 30 Bridge offers simple and low parts count motor controllers.

In a ground referenced system, as shown in Figure 32, the lower N-Channel halves of the bridge can easily be driven by standard CMOS gates if the switching requirements are not too severe. Usually these lower circuits will be pulse width modulated (PWM) whereby the switching speeds of the N-Channel FETs are governed by the driver source/sink current capability. For this example, the MC14504B Hex Level Shifter is ideally suited since it translates the 5.0 V pulse output to the required 15 V FET gate pulse. Secondly, by paralleling two level translators, greater source/sink capability is achieved. The 150  $\Omega$  series gate resistor R3, in conjunction with the rps(on) of the CMOS device (both N and P-Channels) limits the peak gate currents to about ±50 mA. These currents allow the N-Channel power MOSFETs to efficiently switch to frequencies of 15 kHz (higher frequencies would require greater drive capability). Also, these current magnitudes satisfy the

10 mA average metallization limits of the CMOS chip.

Driving the phase steering P-Channel power MOSFETs are also easily achievable as they do not require fast switching. Assuming that the output steering pulses from the micro controller are positive going, all that is required are three interfacing — level translating small signal NPN transistors (Q7-Q9), one for each phase. Since this 60 V breakdown MPM3003 is driving a 48 V motor, these transistors should also be rated at 60 V. Level translations are achieved by turning on the transistors, thus pulling down the P-Channel gates to a bias dictated by the voltage divider R1, R2. For the values shown (1.0 K and 2.7 K respectively), about 13 V of VGS(on) is achieved with R2 dissipating about 150 mW at a 33% duty cycle. The equivalent Thevenin gate impedance of 730  $\Omega$  also allows the P-Channel to switch at an acceptable speed.

For lower voltage systems, the NPN transistors can be eliminated if the micro controller has open-collector NPN transistors that are voltage rated accordingly.

Figure 32. MPM3003 30 Motor Controller